#### **MAX22195**

# High-Speed, Octal, Industrial Digital Input with Parallel Output

#### **General Description**

The MAX22195 translates eight 24V industrial digital inputs to eight CMOS-compatible, parallel outputs. Propagation delay from input-to-output is less than 300ns for all channels. Current-limiters on each digital input greatly reduce power dissipation compared to traditional resistive inputs. The accuracy of these current-limiters minimizes power dissipation while ensuring compliance with the IEC 61131-2 standard. A current-setting resistor allows the MAX22195 to be configured for Type 1, Type 2, or Type 3 inputs. Additionally, the MAX22195 has energyless field-side LED drivers to meet the indicator light requirement of IEC 61131-2 with no additional power dissipation.

The MAX22195 provides a 3.3V integrated voltage regulator. The internal LDO accepts the field supply  $V_{DD24}$  from 7V to 65V. The internal LDO output can supply up to 25mA of current in addition to powering the basic MAX22195 requirements. This MAX22195 LDO current can be used to power digital isolators and other field-side circuits. Alternatively, the MAX22195 can be powered from a 3.0V to 5.5V supply connected to  $V_{DD3}$  pin.

The MAX22195 includes an open-drain READY output that asserts high to indicate the MAX22195 is functional. If the  $V_{DD24}$  field-side supply voltage is too low, or a fault in the current-setting resistor is detected, or the device reaches an over-temperature condition, outputs OP1-OP8 and READY signal are all set to high-impedance.

## **Applications**

- Programmable Logic Controllers

- Industrial Automation

- Process Automation

- Building Automation

#### **Benefits and Features**

- · High-Speed, Industrial Digital Inputs

- · 300ns Maximum Propagation Delay

- ±10ns Maximum Channel-to-Channel Skew

- · Parallel Output for Simultaneous Signal Delivery

- High Integration Reduces BOM Count and Board Space

- Operates Directly from Field Supply (7V to 65V)

- · Compatible with 3.3V or 5V Logic

- 5mm x 5mm, 32-TQFN Package

- Low Power and Low Heat Dissipation

- Low Quiescent Current (1.2mA Maximum)

- · Accurate Input Current-Limiters

- Energyless Field-Side LED Drivers

- Fault Tolerant with Built-In Diagnostics

- Integrated Field-Side Supply Monitor

- Integrated Over-Temperature Monitor

- Current-Setting Resistor Monitor

- Configurability Enables Wide Range of Applications

- Configurable IEC 61131-2 Types 1, 2, 3 Inputs

- Configurable Input Current Limiting from 0.56mA to 3.97mA

- Robust Design

- ±1kV Surge Tolerant using Minimum 1kΩ Resistor

- ±8kV Contact ESD and ±15kV Air Gap ESD Using Minimum 1kΩ Resistor

- -40°C to +125°C Ambient Operating Temperature

Ordering Information appears at end of data sheet.

# **Octal Digital Input with Parallel Output**

# High-Speed, Octal, Industrial Digital Input with Parallel Output

# **Absolute Maximum Ratings**

| V <sub>DD3</sub> to GND  | 0.3V to +6V                     | Continuous Power Dissipation            |                |

|--------------------------|---------------------------------|-----------------------------------------|----------------|

| V <sub>DD24</sub> to GND | 0.3V to +70V                    | Multilayer Board T <sub>A</sub> = +70°C | 2222mW         |

| OP1-OP8                  | 0.3V to V <sub>DD3</sub> + 0.3V | Derate above +70°C                      | 27.80mW/°C     |

| IN1-IN8 to GND           | 40V to +40V                     | Operating Temperature Range             | +125°C         |

| REFDI to GND             | 0.3V to V <sub>DD3</sub> + 0.3V | Maximum Junction Temperature            | +150°C         |

| READY, RDYEN to GND      | 0.3V to +6V                     | Storage Temperature Range               | 65°C to +150°C |

| EXTVM to GND             | 0.3V to +6V                     | Lead Temperature (soldering, 10s)       | +300°C         |

| LED1-LED8 to GND         | 0.3V to +6V                     | Soldering(reflow)                       | +260°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Thermal Characteristics (Note 1)**

**TQFN**

| Junction-to-Ambient Thermal Resistance (θJ <sub>A</sub> ) |        | Junction-to-Case The | ermal Resistance (θJ <sub>C</sub> ) |

|-----------------------------------------------------------|--------|----------------------|-------------------------------------|

| Multilayer Board                                          | 36°C/W | Multilayer Board     |                                     |

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

#### **DC Electrical Characteristics**

$V_{DD3}$  to GND = +3.0V to +5.5V,  $T_A$  = -40°C to +125°C, unless otherwise noted.  $C_L$  on OP1-OP8 = 15pF. Typical values are at  $V_{DD3}$  to GND = +3.3V,  $V_{DD24}$  to GND = +24V, Field Inputs IN1-IN8 = +24V, and  $T_A$  = +25°C. (Note 2)

| PARAMETER                                                      | SYMBOL                   | CONDITIONS                                                                                        | MIN  | TYP  | MAX  | UNITS |

|----------------------------------------------------------------|--------------------------|---------------------------------------------------------------------------------------------------|------|------|------|-------|

| POWER SUPPLIES                                                 | •                        |                                                                                                   |      |      |      |       |

| Supply Voltage                                                 | V <sub>DD24</sub>        | Normal operation                                                                                  | 7    |      | 65   | V     |

| Supply Voltage                                                 | $V_{DD3}$                | Powered from an external power supply                                                             | 3.0  |      | 5.5  | V     |

| Supply Current Powered from V <sub>DD24</sub>                  | I <sub>DD24</sub>        | V <sub>DD24</sub> = 24V, IN1-IN8 = 0V,<br>LED_ = GND, no load on OP1-OP8                          |      | 0.6  | 1.2  | mA    |

| Supply Current Powered from V <sub>DD3</sub>                   | I <sub>DD3</sub>         | V <sub>DD3</sub> = 3.3V, IN1-IN8 = 0V, LED_ = GND, no load on OP1-OP8, V <sub>DD24</sub> floating |      | 0.6  | 1.2  | mA    |

| V <sub>DD3</sub> Undervoltage-Lockout<br>Threshold             | V <sub>UVLO3</sub>       | Powered from $V_{DD3}$ , $V_{DD3}$ rising $V_{DD24}$ floating                                     | 2.4  |      | 2.9  | V     |

| V <sub>DD3</sub> Undervoltage-Lockout<br>Threshold Hysteresis  | V <sub>UVHYST3</sub>     |                                                                                                   |      | 0.07 |      | V     |

| V DEADV Throshold                                              | V <sub>READY_24</sub> VR | V <sub>DD24</sub> rising, EXTVM = GND                                                             | 13.8 | 14.6 | 15.4 | V     |

| V <sub>DD24</sub> READY Threshold                              | V <sub>READY_24VF</sub>  | V <sub>DD24</sub> falling, EXTVM = GND                                                            | 13.3 | 14.1 | 15.0 | V     |

| V <sub>DD24</sub> Undervoltage-Lockout<br>Threshold            | V <sub>UVLO24</sub>      | V <sub>DD24</sub> rising                                                                          | 6.0  |      | 6.8  | V     |

| V <sub>DD24</sub> Undervoltage-Lockout<br>Threshold Hysteresis | V <sub>UVHYST24</sub>    |                                                                                                   |      | 0.45 |      | V     |

| Regulator Output Voltage                                       | V <sub>DD3</sub>         | I <sub>LOAD</sub> = 1mA, V <sub>DD24</sub> = 7V to 65V                                            | 3.0  | 3.3  | 3.6  | V     |

| Line Regulation                                                | dV <sub>DDLINE</sub>     | I <sub>LOAD</sub> = 1mA, V <sub>DD24</sub> = 12V to 24V                                           |      | 0    |      | mV    |

| Load Regulation                                                | dV <sub>DDLOAD</sub>     | $I_{LOAD}$ = 1mA to 10mA, $V_{DD24}$ = 12V                                                        |      | 1    |      | mV    |

# **DC Electrical Characteristics (continued)**

$V_{DD3}$  to GND = +3.0V to +5.5V,  $T_A$  = -40°C to +125°C, unless otherwise noted.  $C_L$  on OP1-OP8 = 15pF. Typical values are at  $V_{DD3}$  to GND = +3.3V,  $V_{DD24}$  to GND = +24V, Field Inputs IN1-IN8 = +24V, and  $T_A$  = +25°C. (Note 2)

| PARAMETER                                             | SYMBOL                    | CONDITIONS                                                                                         | MIN  | TYP  | MAX  | UNITS |

|-------------------------------------------------------|---------------------------|----------------------------------------------------------------------------------------------------|------|------|------|-------|

| Short-Circuit Current Limit                           | I <sub>DD24_SC</sub>      | V <sub>DD24</sub> current when V <sub>DD3</sub> short to GND, V <sub>DD24</sub> = 12V              | 28   | 37.5 | 50   | mA    |

| VDD24 MONITOR                                         |                           |                                                                                                    |      |      |      |       |

| EXTVM Glitch Filter                                   |                           |                                                                                                    |      | 3    |      | μs    |

| EXTVM Threshold Off to On                             | V <sub>24TH</sub> _OFF_ON | V <sub>DD24</sub> rising                                                                           | 0.77 | 0.81 | 0.84 | V     |

| EXTVM Threshold On to Off                             | V <sub>24TH</sub> ON_OFF  | V <sub>DD24</sub> falling                                                                          | 0.74 | 0.79 | 0.82 | V     |

| External EXTVM Selection Threshold                    | EXTVM_SEL                 |                                                                                                    |      | 0.3  |      | V     |

| External EXTVM Selectable V <sub>DD24</sub> Threshold | EXTVM_VDD24               |                                                                                                    | 10   |      | 30   | V     |

| EXTVM Leakage Current                                 | I <sub>EXTVM_L</sub>      |                                                                                                    | -1   |      | 1    | μA    |

| THERMAL SHUTDOWN                                      | <del></del>               |                                                                                                    |      |      |      |       |

| Thermal-Shutdown Threshold                            | T <sub>SHDN</sub>         | VDD3 internal regulator off                                                                        |      | 165  |      | °C    |

| Thermal-Shutdown Hysteresis                           | T <sub>SHDN_HYS</sub>     |                                                                                                    |      | 10   |      | °C    |

| CURRENT LIMITING SETTIN                               | G                         |                                                                                                    |      |      |      |       |

| REFDI Voltage                                         | V <sub>REFDI</sub>        |                                                                                                    |      | 0.61 |      | V     |

| Current-Limit Setting Resistor                        | R <sub>REFDI</sub>        |                                                                                                    | 5.2  | 8.6  | 36   | kΩ    |

| DEEDI DI CI III                                       | DEEDI C                   | Increasing current at pin REFDI                                                                    |      | 550  |      | μA    |

| REFDI Pin Short                                       | REFDI_S                   | Decreasing current at pin REFDI                                                                    |      | 548  |      | μA    |

| REFDI Pin Open                                        | REFDI_O                   | Increasing current at pin REFDI                                                                    |      | 4.46 |      | μA    |

| KEPDI PIII Opeli                                      | KEFDI_O                   | Decreasing current at pin REFDI                                                                    |      | 7.21 |      | μA    |

| IC INPUTS (TYPE 1, 2, 3)                              |                           |                                                                                                    |      |      |      |       |

| Input Current Limit                                   |                           | -40V < V <sub>IN</sub> _ < 0V, V <sub>IN</sub> _ at IN1 - IN8 pins                                 |      | 100  |      | μA    |

| LED On-State Current                                  | I <sub>LED</sub> ON       | $R_{REFDI} = 8.6k\Omega$ , $V_{LED} = 3V$                                                          | 1.5  |      |      | mA    |

| DI Leakage, Current Sources                           |                           | IN1 – IN8 = 28V                                                                                    | 40   | 58   | 80   |       |

| Disabled                                              | IDI_LEAK                  | IN1 – IN8 = 6V                                                                                     | 8    | 11.4 | 16   | μA    |

| Input Threshold Low-to-High                           | V <sub>THP+</sub>         | IN1 – IN8                                                                                          |      | 5.6  | 6    | V     |

| Input Threshold High-to-Low                           | V <sub>THP</sub> _        | IN1 – IN8                                                                                          | 4.4  | 4.7  |      | V     |

| Input Threshold Hysteresis                            | V <sub>INPHYST</sub>      | IN1 – IN8                                                                                          |      | 0.9  |      | V     |

| FIELD INPUTS TYPE 1, 3: (EX                           |                           | S RESISTOR R <sub>IN</sub> = 1.5K $\Omega$ , R <sub>REFDI</sub> = 8.6                              | 6ΚΩ) |      |      |       |

| Field-Input Current Limit                             | I <sub>INLIM</sub>        | 6V (V <sub>THP+</sub> MAX) ≤ VIN_ at the pin ≤ 28V,<br>LED on, R <sub>REFDI</sub> = 8.6kΩ (Note 3) | 2.15 | 2.40 | 2.65 | mA    |

| Field Input Threshold<br>Low-to-High                  | V <sub>INF+</sub>         | $R_{REFDI}$ = 8.6kΩ, 1.5kΩ external series resistor                                                |      |      | 10   | V     |

| Field Input Threshold<br>High-to-Low                  | V <sub>INF</sub> -        | $R_{REFDI}$ = 8.6kΩ, 1.5kΩ external series resistor                                                | 8    |      |      | V     |

|                                                       | 1                         |                                                                                                    | 1    |      |      | 1     |

# **DC Electrical Characteristics (continued)**

$V_{DD3}$  to GND = +3.0V to +5.5V,  $T_A$  = -40°C to +125°C, unless otherwise noted.  $C_L$  on OP1-OP8 = 15pF. Typical values are at  $V_{DD3}$  to GND = +3.3V,  $V_{DD24}$  to GND = +24V, Field Inputs IN1-IN8 = +24V, and  $T_A$  = +25°C. (Note 2)

| PARAMETER                                                        | SYMBOL                 | CONDITIONS                                                                                         | MIN                       | TYP  | MAX                       | UNITS |

|------------------------------------------------------------------|------------------------|----------------------------------------------------------------------------------------------------|---------------------------|------|---------------------------|-------|

| FIELD INPUTS TYPE 2: (EXTI                                       | ERNAL SERIES           | RESISTOR R <sub>IN</sub> = $1K\Omega$ , $R_{REFDI} = 5.2K\Omega$                                   | 2)                        |      |                           |       |

| Field-Input Current Limit                                        | I <sub>INLIM</sub>     | 6V (V <sub>THP+</sub> MAX) ≤ VIN_ at the pin ≤ 28V,<br>LED on, R <sub>REFDI</sub> = 5.2kΩ (Note 3) | 3.55                      | 3.97 | 4.39                      | mA    |

| Field Input Threshold<br>Low-to-High                             | V <sub>INF+</sub>      | $R_{REFDI}$ = 5.2kΩ, 1kΩ external series resistor                                                  |                           |      | 10                        | V     |

| Field Input Threshold<br>High-to-Low                             | V <sub>INF-</sub>      | $R_{REFDI}$ = 5.2kΩ, 1kΩ external series resistor                                                  | 8                         |      |                           | V     |

| LOGIC INPUT (RDYEN)                                              |                        |                                                                                                    |                           |      |                           |       |

| Input Logic-High Voltage                                         | V <sub>IH</sub>        |                                                                                                    | 0.7 x<br>V <sub>DD3</sub> |      |                           | V     |

| Input Logic-Low Voltage                                          | V <sub>IL</sub>        |                                                                                                    |                           |      | 0.3 x<br>V <sub>DD3</sub> | V     |

| Input Pulldown Resistance                                        | R <sub>PD</sub>        |                                                                                                    |                           | 199  |                           | kΩ    |

| LOGIC OUTPUT (OP1-OP8, R                                         | EADY)                  |                                                                                                    | ,                         |      |                           |       |

| Output Logic-High Voltage                                        | V <sub>OH</sub>        | Sourcing 4mA                                                                                       | V <sub>DD3</sub> - 0.4    |      |                           | V     |

| Output Logic-Low Voltage                                         | V <sub>OL</sub>        | Sinking 4mA                                                                                        |                           |      | 0.4                       | V     |

| Output Leakage Current                                           | I <sub>OPL</sub>       |                                                                                                    | -1                        |      | 1                         | μΑ    |

| DYNAMIC CHARACTERISTIC                                           | S (OP1-OP8)            |                                                                                                    |                           |      |                           |       |

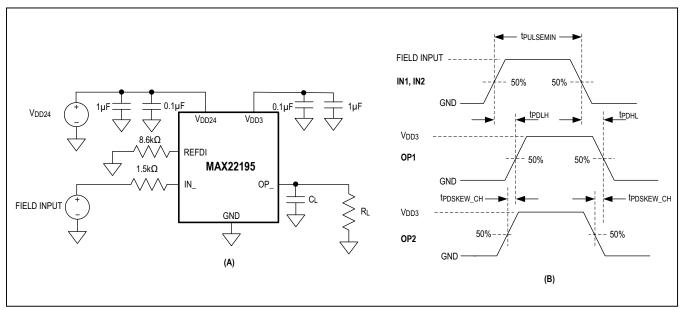

| Propagation Delay<br>Low-to-High ( <u>Figure 1</u> )             | t <sub>PDLH</sub>      | IN_ to OP_, R <sub>IN</sub> = 1.5kΩ,<br>IN_ = 11V and 36V                                          |                           |      | 300                       | ns    |

| Propagation Delay<br>High-to-Low ( <u>Figure 1</u> )             | t <sub>PDHL</sub>      | IN_ to OP_, R <sub>IN</sub> = 1.5kΩ,<br>IN_ = 11V and 36V                                          |                           |      | 300                       | ns    |

| Propagation Delay Skew<br>Channel-to-Channel ( <u>Figure 1</u> ) | t <sub>PDSKEW_CH</sub> | IN_ to OP_, R <sub>IN</sub> = 1.5kΩ,<br>IN_ = 11V and 36V                                          | -10                       |      | 10                        | ns    |

| Propagation Delay Skew<br>Part-to-Part ( <u>Figure 1</u> )       | tpdskew_part           | IN_to OP_, $R_{IN}$ = 1.5k $\Omega$ , IN_ = 11V and 36V, All conditions are the same between parts | -200                      |      | +200                      | ns    |

| D                                                                | t <sub>PDJ_R</sub>     | Output Rising, V <sub>DD3</sub> = 3.3V, IN_ = 24V                                                  |                           | 40   |                           | ps    |

| Propagation Delay Jitter                                         | t <sub>PDJ_F</sub>     | Output Falling, V <sub>DD3</sub> = 3.3V, IN_ = 24V                                                 |                           | 50   |                           | ps    |

| Detectable Pulse Width (Figure 1)                                | t <sub>PW</sub>        | IN_ to OP_, R <sub>IN</sub> = 1.5kΩ,<br>IN_ = 11V and 36V                                          | 220                       |      |                           | ns    |

| Pulse Width Distortion                                           | PWD                    | tpdlh - tpdhl                                                                                      | 0                         |      | 180                       | ns    |

**Note 2:** All units are production tested at  $T_A = +25$ °C. Specifications over temperature are guaranteed by design.

**Note 3:** External resistor REFDI is selected to set any desired current limit between 0.56mA to 3.97mA (typical values). The current limit accuracy of ±10.6% is guaranteed for values greater or equal to 2mA.

Figure 1. Test Circuit (A) and Timing Diagram (B)

# **ESD** and **EMC** Characteristics

| PARAMETER                         | SYMBOL            | CONDITIONS                                                                                                    | VALUE | UNITS |

|-----------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------|-------|-------|

| Surge Line-to-Line Line-to-Ground |                   | IEC 61000-4-5, 1.2/50 $\mu$ s pulse, minimum 1k $\Omega$ resistor in series with IN - IN8 with respect to GND | ±2    |       |

|                                   |                   | IEC 61000-4-5, 1.2/50 $\mu$ s pulse, minimum 1k $\Omega$ resistor in series with IN - IN8 with respect to GND | ±1    |       |

|                                   | Human Body Model  | All Pins                                                                                                      | ±2    | kV    |

| ESD Contact Discharge             |                   | IEC 61000-4-2, minimum 1k $\Omega$ resistor in series with IN - IN8 with respect to GND                       | ±8    |       |

|                                   | Air-Gap Discharge | IEC 61000-4-2, minimum 1k $\Omega$ resistor in series with IN - IN8 with respect to GND                       | ±15   |       |

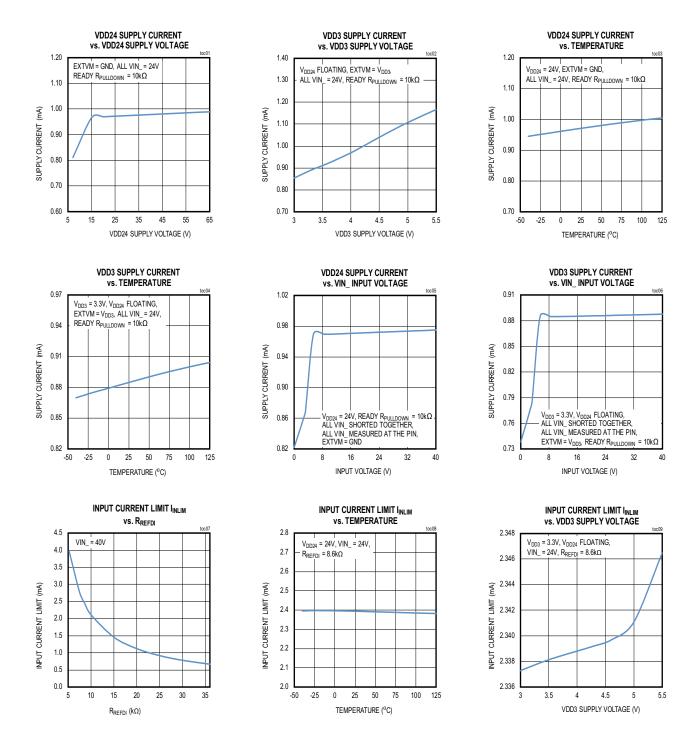

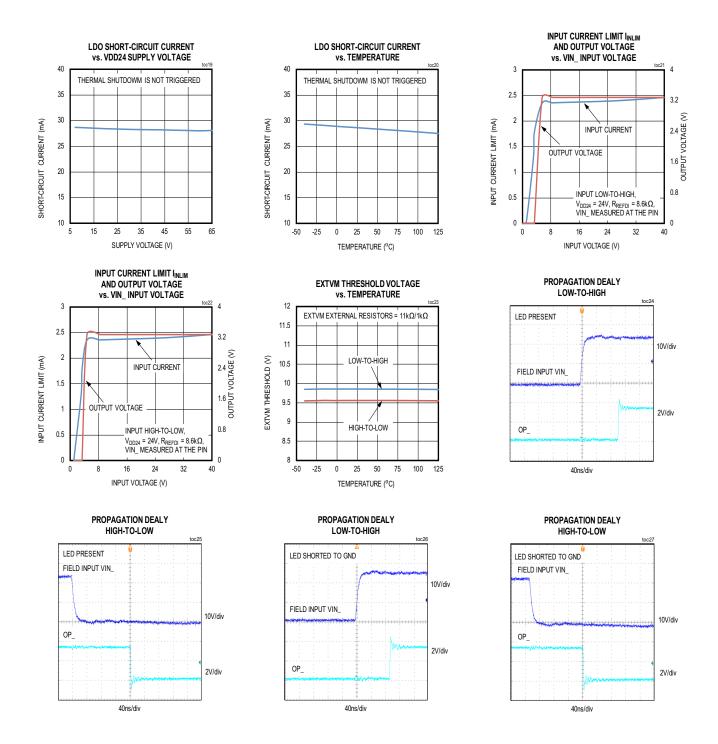

## **Typical Operating Characteristics**

$V_{DD24} = 24V, V_{DD3} = 3.3V, T_A = +25^{\circ}C, R_{REFDI} = 8.6k\Omega \text{ or } 5.2k\Omega, R_{IN} = 1.5k\Omega \text{ or } 1k\Omega, \text{ unless otherwise noted}.$

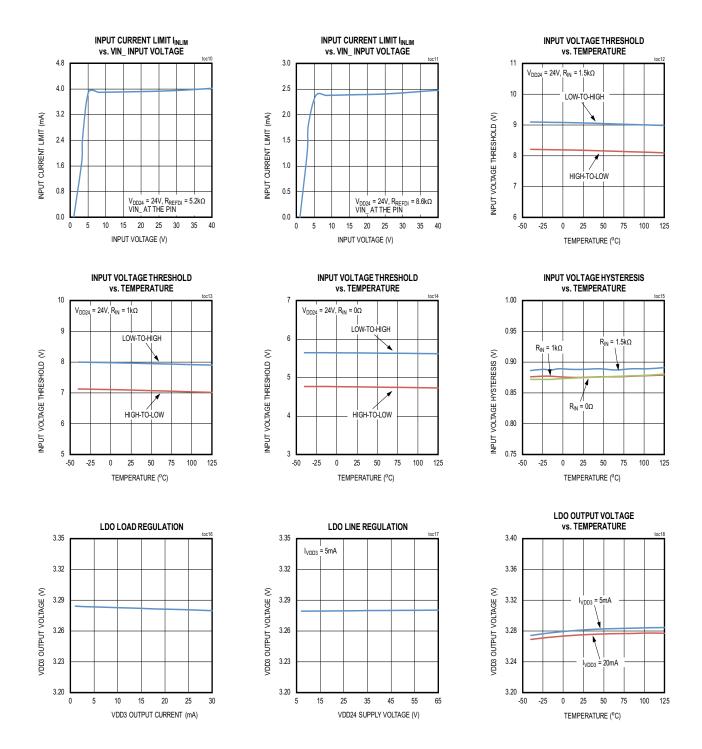

# **Typical Operating Characteristics (continued)**

$V_{DD24} = 24V, \ V_{DD3} = 3.3V, \ T_A = +25^{\circ}C, \ R_{REFDI} = 8.6k\Omega \ or \ 5.2k\Omega, \ R_{IN} = 1.5k\Omega \ or \ 1k\Omega, \ unless \ otherwise \ noted.$

## **Typical Operating Characteristics (continued)**

$V_{DD24} = 24V, V_{DD3} = 3.3V, T_A = +25^{\circ}C, R_{REFDI} = 8.6k\Omega \text{ or } 5.2k\Omega, R_{IN} = 1.5k\Omega \text{ or } 1k\Omega, \text{ unless otherwise noted}.$

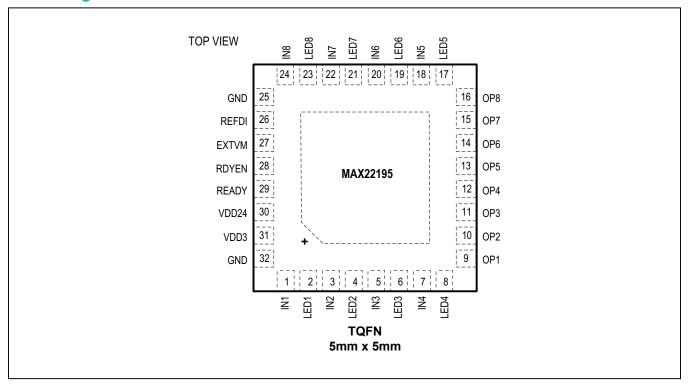

# **Pin Configurations**

# **Pin Description**

| PIN                        | NAME                    | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|----------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| POWER SUI                  | POWER SUPPLY            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 30                         | V <sub>DD24</sub>       | 24V Field Supply. Bypass to GND with 0.1µF capacitor in parallel with 1µF capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 31                         | V <sub>DD3</sub>        | 3.3V output from integrated LDO when powered from $V_{DD24}$ , or 3.0 - 5.5V supply input when $V_{DD24}$ not driven. Bypass to GND with 0.1µF capacitor in parallel with 1µF capacitor. If powering $V_{DD3}$ from an external supply, leave $V_{DD24}$ floating. $V_{DD3}$ output is turned off during thermal shutdown.                                                                                                                                                                                |  |  |  |  |

| 25, 32                     | GND                     | Ground Return for All Signals and the Power Supplies                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| EP                         | -                       | Exposed Pad. Connect to GND. Solder entire exposed pad area to ground plane with multiple vias for best thermal performance. EP = exposed pad on the back of the package                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| ANALOG PI                  | NS                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 27                         | EXTVM                   | Connect EXTVM to GND to use internal thresholds (14V, typical) for $V_{DD24}$ voltage monitoring. Connect EXTVM to external resistive divider to set external thresholds for $V_{DD24}$ voltage monitoring. Connect EXTVM to $V_{DD3}$ to disable $V_{DD24}$ voltage monitoring at READY pin if the device is powered by $V_{DD3}$ .                                                                                                                                                                      |  |  |  |  |

| 26                         | REFDI                   | Digital Input Current-Limit Reference Resistor. For 24V Type 1 and Type 3 inputs, place a $8.6k\Omega$ resistor from REFDI to GND. For Type 2 inputs, place a $5.2k\Omega$ resistor from REFDI to GND.                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| FIELD INPU                 | TS PINS                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 1,3,5,7,18,<br>20,22,24    | IN1-IN8<br>respectively | Field Inputs. For 24V Type 1 and Type 3 inputs, place a $1.5k\Omega$ MELF resistor between the field input and IN_ pin. For Type 2 inputs, place a $1k\Omega$ MELF resistor between the field input and IN_ pin.                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 2,4,6,8,17,<br>19,21,23    | LED1-LED8 respectively  | Energyless LED Driver Outputs. Connect to GND if LEDs are not used.                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| LOGIC PINS                 |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 9,10,11,12,<br>13,14,15,16 | OP1-OP8 respectively    | Logic Outputs. Indicate the state (high or low) of IN1-IN8. High level is V <sub>DD3</sub> . Low level is GND. If READY pin output is low, OP1-OP8 are high-impedance.                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 28                         | RDYEN                   | Ready Enable. Has a weak internal pulldown. Assert high to enable the READY output. Cascade the READY signal of multiple devices through a single isolator or a microcontroller input pin by connecting the READY output of each device to the RDYEN input of the next device in the chain. READY from the last device in the chain drives the isolator input, or the microcontrol GPI.                                                                                                                   |  |  |  |  |

| 29                         | READY                   | Open-drain output. Connect a pulldown resistor between READY and GND pin. Assert high to indicate the device is functional and the outputs are valid. The following conditions must be met for READY to assert high:  1. V <sub>DD3</sub> is above the UVLO threshold.  2. REFDI is not open or shorted to GND.  3. MAX22195 is not in Thermal Shutdown.  4. RDYEN is high.  5. V <sub>DD24</sub> is valid if the device is powered by V <sub>DD24</sub> and EXTVM is not connected to V <sub>DD3</sub> . |  |  |  |  |

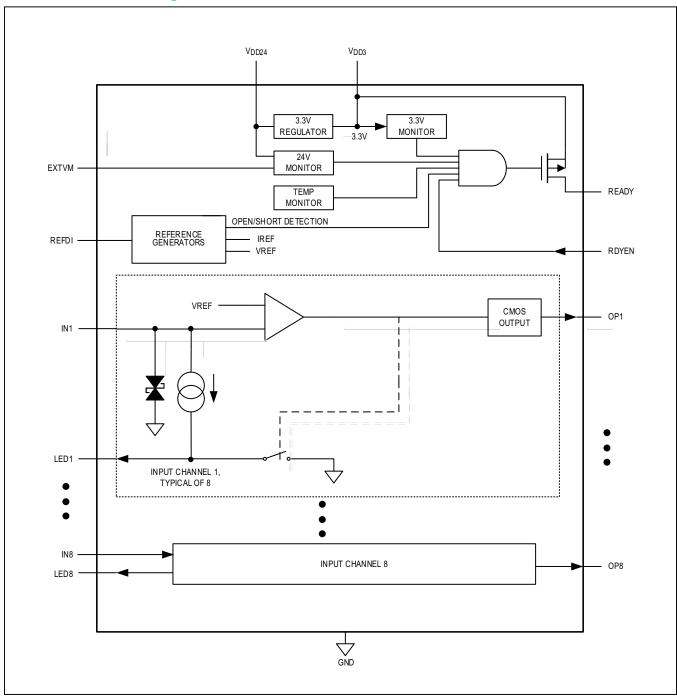

# **Functional/Block Diagram**

#### **Detailed Description**

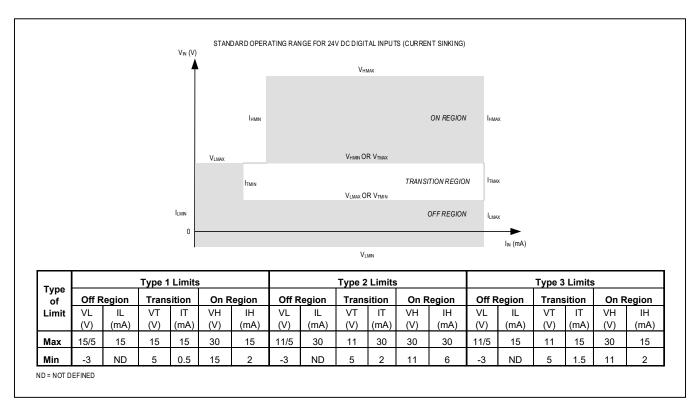

The MAX22195 senses the state (on, high or off, low) of each input (IN1-IN8). The voltages at the IN1-IN8 input pins are compared against internal references to determine whether the sensor is on (logic 1) or off (logic 0). Placing a  $8.6k\Omega$  current-setting resistor between REFDI and GND, and a  $1.5k\Omega$  resistor in series with each input ensures that the current at the on and off trip points as well as the voltage at the trip points satisfy the requirements of IEC 61131-2 for Type 1 and Type 3 inputs (Figure 2). The current sunk by each input pin rises linearly with input voltage until the level set by the current-limiter is reached; any voltage increase beyond this point does not increase the input current. Limiting the input current ensures compliance with IEC 61131-2 while significantly reducing power dissipation compared to traditional resistive inputs.

using this equation:

$R_{REFDI} = 20V/I_{INLIM}$

The current-setting resistor R<sub>RFFDI</sub> can be calculated

#### **RDYEN and READY Monitor**

The READY output is used to signal a logic-side controller that the field-side circuit is working. This allows the controller to distinguish from a valid reading of eight low inputs or an invalid reading caused by a field-side fault such as loss of power. The READY output is asserted high when the following five conditions are met: the UVLO voltage threshold for  $V_{DD3}$  is exceeded; the  $V_{DD24}$  field supply requirement is met as set by internal thresholds or EXTVM external thresholds if enabled; the device is not in thermal shutdown; current through the REFDI pin is in a reasonable range (7.21 $\mu$ A to 550 $\mu$ A); and the RDYEN is high.

Ready Enable RDYEN is used to cascade other READY signals through to a single digital isolation channel or a microcontroller GPI pin. Connect the READY output of one device to the RDYEN input of the next device in the chain. Connect the final READY output to a digital isolator or a microcontroller GPI pin. All READY signals must be high for the final READY signal to go high. READY is an open-drain PMOS output, driven to  $V_{DD3}$  for a high output and set at high-impedance for a low output. Refer to Typical Operating Circuit for details.

Outputs OP1 - OP8 are high-impedance when READY is low.

Figure 2. Switching Characteristics for IEC 61131-2 Type 1, 2, and 3 24VDC Digital Inputs

#### External VDD24 Voltage Monitor

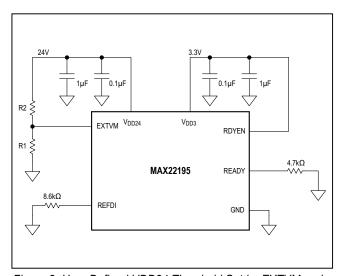

The EXTVM input controls how the VDD24 field supply affects the READY output. When EXTVM is connected to V<sub>DD3</sub>, the status of the V<sub>DD24</sub> field supply becomes a don't-care in the decision to assert READY. This is useful when the MAX22195 is being powered directly from a 3.3V supply on  $V_{DD3}$  and  $V_{DD24}$  is not in use. When EXTVM is connected to GND, the voltage on V<sub>DD24</sub> must be above the nominal 14V threshold before READY asserted high. To use an user-defined V<sub>DD24</sub> supply voltage threshold, use an external resistive divider to apply an analog voltage directly to EXTVM. The voltage at EXTVM must be greater than the threshold, 0.81V (V<sub>REF</sub>) nominal, before READY asserted high. Figure 3 shows an example of the V<sub>DD24</sub> being monitored with the use of external resistive divider to set a nominal threshold before READY asserted high.

$V_{DD24} = V_{REF} (1 + (R2/R1))$

#### **Short/Open Detection at REFDI Pin**

Short or open detection at REFDI pin is implemented by monitoring the current set by REFDI pin.When more than 550µA current is detected, meaning a short at REFDI, all input channels are disabled, but REFDI buffer is still on to keep the detection. When less than 7.21µA current is detected, meaning an open at REFDI, the 2mA minimum input current is not guaranteed. When open or short at REFDI pin is detected, the READY pin is not asserted.

Figure 3. User-Defined VDD24 Threshold Set by EXTVM and External Resistive Divider

#### **Energyless LED Drivers**

When IN\_ is determined to be on, its input current is diverted to the LED\_ pin and flows from that pin to GND. Placing an LED between LED\_ and GND provides an indication of the input state without increasing overall power dissipation. If the indicator LEDs are not used, connect LED to GND.

#### **Surge Protection**

Placing a minimum  $1k\Omega$  pulse withstanding or MELF resistor in series with each input allows the robust ESD structures on each field-input pins to provide surge protection up to  $\pm 2kV$  line-to-line or  $\pm 1kV$  line-to-ground. During a surge event, the protection at IN\_ pins clamps the input to reduce power dissipation, and releases the input when the surge current has dissipated.

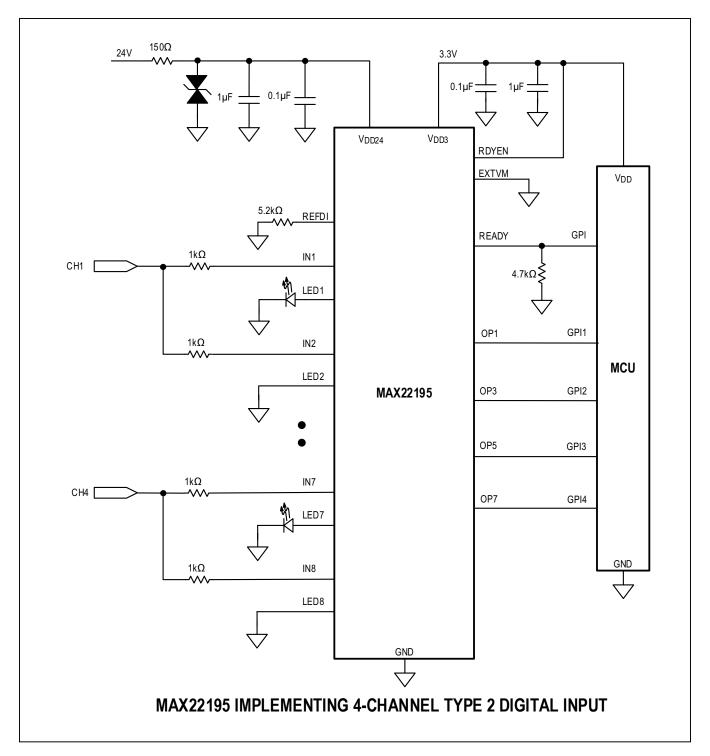

#### Type 2 Sensor Inputs

The additional input current (6mA min) and associated power dissipation of Type 2 input require the use of two MAX22195 inputs in parallel. The current of each channel is set to a nominal 3.97mA (7.9mA total) by placing a  $5.2k\Omega$ resistor from REFDI to GND. The proper voltage drop across the input resistor is maintained by reducing the resistance from  $1.5k\Omega$  to  $1k\Omega$  for each MAX22195 input channel. If lower input current is desired, the REFDI resistor can be increased to  $5.76k\Omega$  or higher as long as the 6mA minimum input current for Type 2 is met. For proper surge protection, it is important that each MAX22195 input has its own resistor. Any two MAX22195 channels may be used; they need not be continuous (Figure 4). Either channel may be read to determine the input state. The additional power dissipation from this Type 2 configuration reduces the maximum ambient operating temperature to 120°C, when all inputs are at 30V, and the MAX22195s are powered from a 30V field supply and there is no additional load on  $V_{DD3}$ .

#### Thermal Considerations

The MAX22195 will operate at an ambient temperature of 125°C on a properly designed multilayer PC board. Operating at higher voltages, or with heavy output loads such as optical isolators will increase power dissipation and reduce the maximum allowable operating temperature. See <a href="Package Thermal Characteristics">Package Thermal Characteristics</a> section and <a href="Absolute Maximum Ratings">Absolute Maximum Ratings</a> section for safety operation temperature and maximum power dissipation.

The MAX22195 will be in thermal shutdown when the thermal shutdown temperature threshold is exceeded. During thermal shutdown, the internal voltage regulator, input channels, and REFDI circuitry are all turned off.

Figure 4. Implementing Type 2 Digital Inputs with MAX22195

## **Applications Information**

#### **Power Supply Decoupling**

To reduce ripple and the chance of introducing data errors, bypass  $V_{DD24}$  and  $V_{DD3}$  with a  $0.1\mu F$  low-ESR ceramic capacitor in parallel with  $1\mu F$  ceramic capacitor to GND. Place the bypass capacitors as close as possible to the power supply input pins.

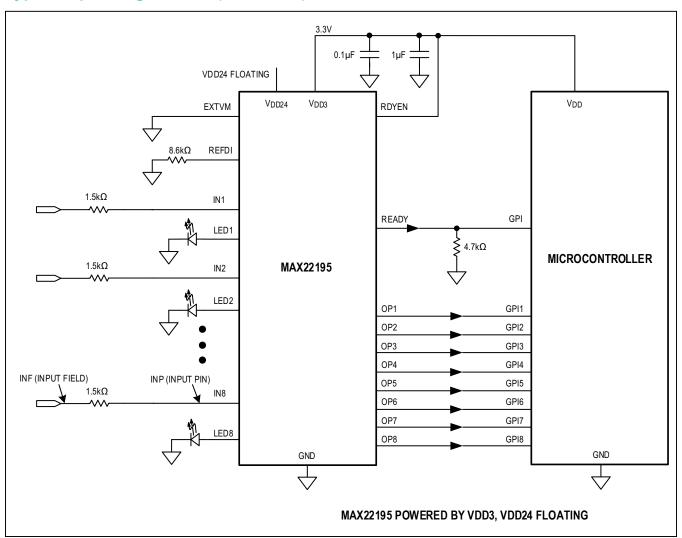

#### Powering MAX22195 with V<sub>DD3</sub>

The MAX22195 can alternatively be powered using a 3.0-5.5V supply connected to the  $V_{DD3}$  pin. In this case, a 24V supply is no longer needed and the  $V_{DD24}$  pin must be left floating (not connected), see <u>Typical Operating Circuit</u> for details. This configuration has lower power consumption and heat dissipation since the on-chip LDO voltage regulator is disabled (the  $V_{DD24}$  undervoltage lockout is below threshold and automatically disables the LDO).

#### **PCB Layout Recommendations**

The PCB designer should follow some critical recommendations in order to get the best prformance from the design.

Keep the input/output traces as short as possible.

Avoid using vias on the signals to make low-

inductance paths.

Have a solid ground plane underneath the entire exposed pad (EP) area with multiple thermal vias for best thermal performance.

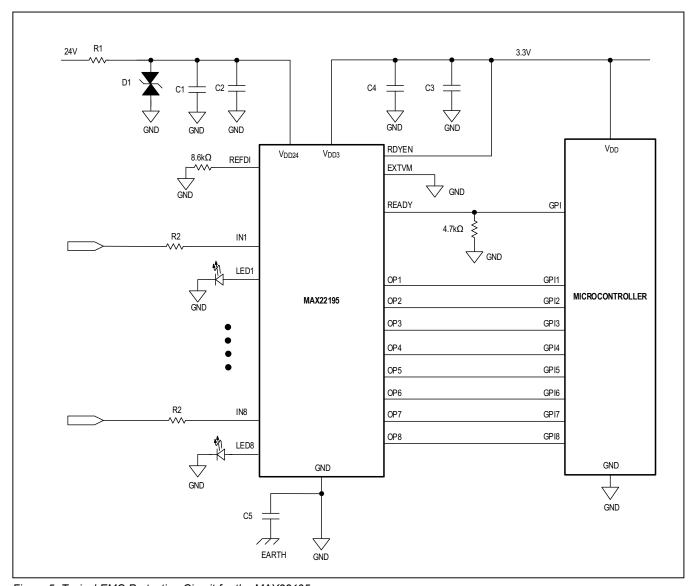

#### **EMC Standard Compliance**

The MAX22195 is required to operate reliably in harsh industrial environment. Maxim does board-level immunity testing for products, such as the MAX22195 to address IEC 61000-4-x Transient Immunity Standards:

- IEC 61000-4-2 Electrostatic Discharge (ESD)

- IEC 61000-4-4 Electrical Fast Transient/Burst (EFT)

- IEC 61000-4-5 Surge Immunity

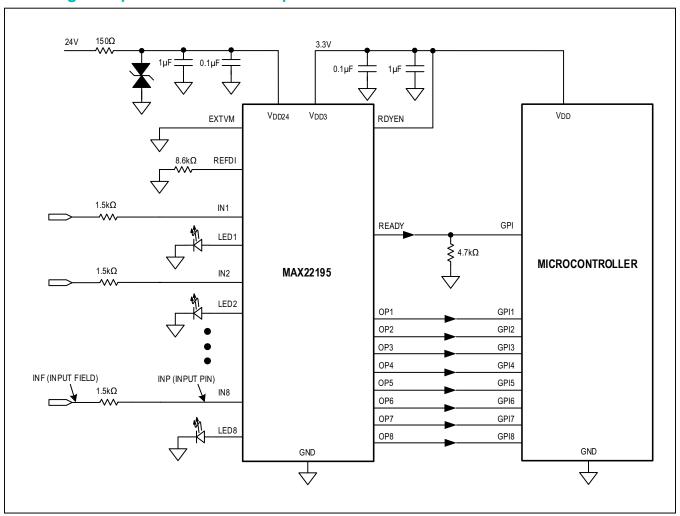

Maxim's proprietary process technology provides high ESD support with internal ESD structures, but external components are also required to absorb energy from burst and surge transients. The circuit with external components shown in <a href="Figure 5">Figure 5</a> allows the device to operate in harsh industrial environments. Components were chosen to assist in suppression of voltage burst and surge transients, allowing the system to meet or exceed international EMC requirements. The system shown in <a href="Figure 5">Figure 5</a>, using the components shown in <a href="Table 1">Table 1</a>, is designed to be robust against IEC ESD, EFT, and Surge specifications.

**Table 1. Recommended Components for EMC compliance**

| COMPONENT           | DESCRIPTION                                                                        | REQUIRED/RECOMMENDED |

|---------------------|------------------------------------------------------------------------------------|----------------------|

| C1                  | 1μF, 100V ceramic capacitor                                                        | Required             |

| C2                  | 0.1μF, 100V low-ESR ceramic capacitor                                              | Required             |

| C3                  | 1μF, 10V ceramic capacitor                                                         | Required             |

| C4                  | 0.1μF, 10V low-ESR ceramic capacitor                                               | Required             |

| C5                  | 3.3nF, safety rated Y capacitor (2220)                                             | Recommended          |

| D1                  | Bidirectional TVS diode (SMAJ33CA or SM30T39AY)                                    | Recommended          |

| R1                  | 150Ω, 1W pulse withstanding resistor (CMB0207 or similar)                          | Recommended          |

| R2                  | 1.5k $\Omega$ or 1k $\Omega$ , 1W pulse withstanding resistor (CMB0207 or similar) | Required             |

| All other Resistors | 1/8W resistor                                                                      | Required             |

| D1 - D8             | LEDs for visual input status indication                                            | Recommended          |

Figure 5. Typical EMC Protection Circuit for the MAX22195

#### **Test Levels and Methodology**

The MAX22195 is tested for Transient Immunity Standards, as specified in IEC 61000-4-x. These tests are for industrial equipment which are subjected to various transients. The three main tests are:

- IEC 61000-4-2: This ESD standard covering surges of tens of ns duration, is more stressful than other standards such as Human Body Model (HBM) or Machine Model (MM), both of which are tested as standard for all Maxim products.

- IEC 61000-4-4: This standard indicates the capability of the device or equipment to survive repetitive electrical fast transients and bursts which often occur from arcing contacts in switches and relays.

- IEC 61000-4-5: This standard indicates the capability

of the device or equipment to survive surges caused

by events such as lightning strikes or industrial

power surges caused by switching heavy loads or

short-circuit fault conditions.

In all these tests, the part or DUT is soldered onto an application board with bypass capacitors on power supply pins. In the case of the MAX22195, the standard Evaluation Kit (MAX22195EVKIT#) is used for these tests. Table 2 details all equipment used in the Surge, EFT and ESD tests. The test results are shown in Table 3.

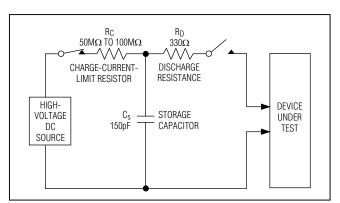

#### IEC 61000-4-2 Electrostatic Discharge (ESD):

This is an international standard which gives immunity requirements and test procedures related to "electrostatic discharge".

**Contact Discharge Method:** The electrode of the test generator is held in contact with the EUT, and the discharge actuated by the discharge switch within the generator.

**Air-Gap Discharge Method:** The charged electrode of the generator is brought close to the EUT, and the discharge actuated by a spark to the EUT.

An ESD Test Generator is used with a "sharp point' to make direct connection to the EUT (pin) under test for Contact ESD testing, and a "round tip" is added to the generator for air-gap ESD testing.

| Output Voltage                    | Up to ±8kV (nominal) for contact<br>discharge<br>Up to ±15kV (nominal) for air-gap<br>discharge |

|-----------------------------------|-------------------------------------------------------------------------------------------------|

| Polarity of the Output<br>Voltage | Positive and negative                                                                           |

| Holding time                      | At least 5 seconds                                                                              |

| Number of Applications            | 10 consecutive ESD discharges for each polarity                                                 |

# **Table 2. Equipment Used for EMC Tests**

| EQUIPMENT                             | DESCRIPTION                                                    | TEST(S)                     |

|---------------------------------------|----------------------------------------------------------------|-----------------------------|

| MAX22195EVKIT#                        | Evaluation board with MAX22195 and recommend operating circuit | All                         |

| ESD Test Generator                    | Teseq NSG438 with Air-Gap Discharge Tip 403-826                | Contact ESD and Air-Gap ESD |

| EFT/Surge Generator                   | Haefely Technology ECOMPACT4                                   | EFT and Surge               |

| Signal and Data Line Coupling Network | Teseq CDN 117                                                  | Surge                       |

| Coupler with 0.5µF Capacitor          | INA 174A                                                       | Surge                       |

| Burst/EFT Data Line Coupling Clamp    | Teseq CDN 3425                                                 | EFT                         |

### **Table 3. Transient Immunity Test Results**

| TEST                                        | RESULT         |       |

|---------------------------------------------|----------------|-------|

|                                             | Contact ESD    | ±8kV  |

| IEC 61000-4-2 Electrostatic Discharge (ESD) | Air Gap ESD    | ±15kV |

|                                             | Line-to-Line   | ±2kV  |

| IEC 61000-4-5 Surge Immunity                | Line-to-Ground | ±1kV  |

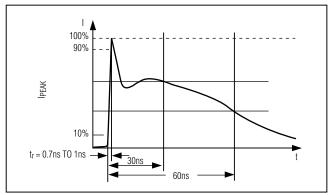

Transient Voltage Suppression (TVS) diodes are used to meet the ESD transient immunity requirements of IEC 61000-4-2. These diodes have extremely fast response times in order to respond to the 1ns rise time of the ESD pulse. Figure 6a shows the IEC 61000-4-2 model and Figure 6b shows the current waveform for IEC 61000-4-2 ESD Contact Discharge Test. The TVS diode clamps the incoming transients at a safe level to avoid damage to the semiconductor device.

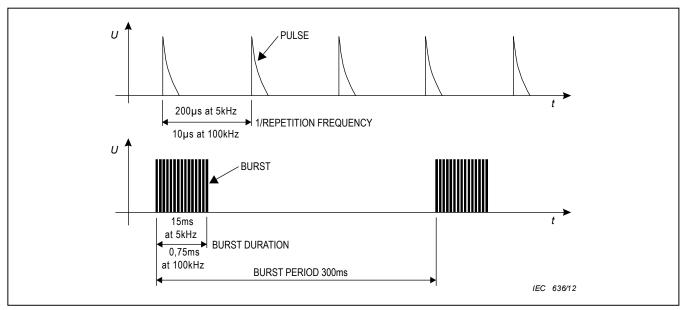

#### IEC 61000-4-4 Electrical Fast Transient/Burst (EFT)

An EFT/Surge Generator with an output voltage range up to  $\pm 1 \text{kV}$  with  $50\Omega$  load is used to generate the voltage waveforms defined by the IEC specification. The capaci-

Figure 6a. Test Circuit

tive coupling clamp provides the ability to couple the fast transients (burst) from the EFT Generator to the pins of the MAX22195 without any galvanic connection to the MAX22195's pins. The waveform is shown in Figure 7.

| Polarity             | Positive and negative                                        |

|----------------------|--------------------------------------------------------------|

| Test Voltage         | Up to 1kV                                                    |

| Repetition Frequency | 5kHz                                                         |

| Burst Duration       | 15ms (at 5 kHz)                                              |

| Burst Period         | 300ms                                                        |

| Signal Applied To    | Input ports (IN_) and Voltage<br>Supply (V <sub>DD24</sub> ) |

| Test Duration        | 60 seconds                                                   |

Figure 6b. Test Waveform

Figure 7. Electrical Fast Transient/Burst Waveform

#### IEC 61000-4-5 Surge Immunity

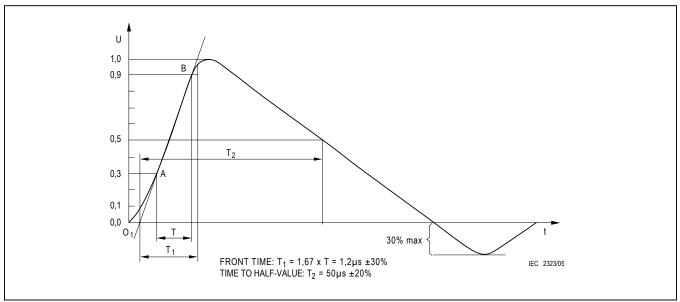

This standard specifies different wave generator specifications. The 1.2/50µs combination wave generator is used for testing ports intended for power lines and short-distance signal connections. This is the test Maxim uses and the waveform is shown in Figure 8.

| Polarity            | Positive and negative                          |

|---------------------|------------------------------------------------|

| Test Voltage        | Up to ±2kV                                     |

| Waveform parameters | Front time 1.2µs<br>Time to half value 50µs    |

| Signal applied to   | Input port-to-Input port, Input port-to-Ground |

| Repetition Rate     | 1 per minute                                   |

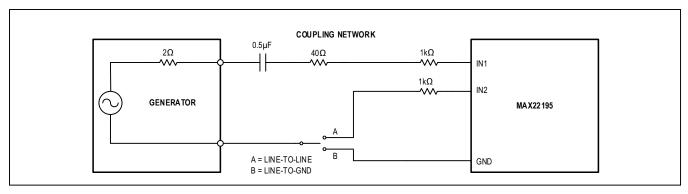

The standard defines 6 classes of test levels which depend on the installation conditions (see Annex A, Table A.1 in IEC 61000-4-5 standard). The class determines the protection with corresponding voltage levels from 25V to 4kV. In addition this defines the coupling mode (Line-to-Line or Line-to-Ground) and the source impedance (Zs) required. The class which most closely fits the applications using products such as MAX22195 are Class 3 for Unsymetrical operated circuits/lines with suggested test levels of ±2kV for Line-to-Line and ±1kV for Line-to-Ground.

The selection of source impedance is discussed in Annex B of IEC 61000-4-5 with recommended Zs of 42 $\Omega$ . Since the generator has an internal impedance of 2 $\Omega$ , an external 40 $\Omega$  resistor is used in series with the generator, as shown in simplified version in Figure 9.

Figure 8. 1.2/50µs Surge Voltage Waveform

Figure 9. Surge Testing Method

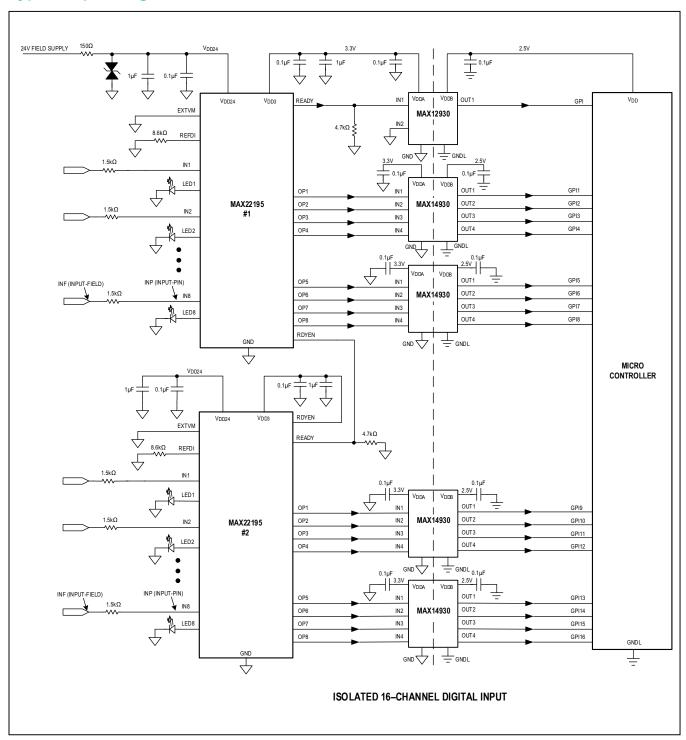

# **Typical Operating Circuits**

# **Typical Operating Circuits (continued)**

# **Chip Information**

PROCESS: BICMOS

# **Ordering Information**

| PART         | TEMP RANGE      | PIN-PACKAGE |

|--------------|-----------------|-------------|

| MAX22195ATJ+ | -40°C to +125°C | 32-TQFN     |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

## **Package Information**

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE | PACKAGE | OUTLINE | LAND        |

|---------|---------|---------|-------------|

| TYPE    | CODE    | NO.     | PATTERN NO. |

| 32-TQFN | T3255+6 | 21-0140 | 90-0603     |

### MAX22195

# High-Speed, Octal, Industrial Digital Input with Parallel Output

# **Revision History**

|   | REVISION<br>NUMBER | REVISION DATE | DESCRIPTION                                                                                                                                | PAGES<br>CHANGED |

|---|--------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| ĺ | 0                  | 5/18          | Initial release                                                                                                                            | _                |

|   | 1                  | 7/18          | Updated Benefits and Features section, Electrical Characteristics table, Pin Description table, Detailed Description section, and Figure 5 | 1, 4, 5, 11, 14  |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.